IBM

# The PowerPC Compiler Writer's Guide

Edited by: Steve Hoxey Faraydon Karim Bill Hay Hank Warren

> Warthman Associates

© International Business Machines Corporation 1996. All rights reserved. 1-96. Printed in the United State of America.

This notice applies to The PowerPC Compiler Writer's Guide, dated January 1996. The following paragraphs do not apply in any country or state where such provisions are inconsistent with local law: The specifications in this publication are subject to change without notice. The publication is provided "AS IS." International Business Machines Corporation (hereafter "IBM") does not make any warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. Unless specifically set forth herein, there are no express or implied patent, copyright or any other intellectual property rights or licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document. Permission is hereby granted to the owner of this publication to copy and distribute only the code examples contained in this publication for the sole purpose of enabling system and software implementers to use PowerPC microprocessors, and for no other purpose. IBM does not warrant that the contents of this publication or the accompanying code examples, whether individually or as one or more groups, will meet your requirements or that the publication or the accompanying code examples are error-free. This publication could include technical inaccuracies or typographical errors. Changes may be made to the information herein; these changes may be incorporated in new editions of the publication.

Notice to U.S. Government Users—Documentation Related to Restricted Rights—Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corporation.

The following are registered trademarks of the IBM Corporation: IBM and the IBM logo.

The following are trademarks of the IBM Corporation: IBM Microelectronics, POWER, RISC System/6000, PowerPC, PowerPC logo, PowerPC 601, PowerPC 603, PowerPC 604. PowerPC™ microprocessors are hereinafter sometimes referred to as "PowerPC".

The following are trademarks of other companies: SPECfp92, SPECint92, SPECfp95, and SPECint95 are trademarks of Standard Performance Evaluation Corporation.

Requests for copies of this publication should be made to the office shown below. IBM may use, disclose or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6531 Tel: (800) POWERPC Fax Service 415-855-4121

The IBM home page can be found at: http://www.ibm.com The IBM Microelectronics Division PowerPC home page can be found at: http://www.chips.ibm.com/products/ppc

Library of Congress Catalog Card Number: 95-62115 ISBN 0-9649654-0-2

Published for IBM by: Warthman Associates 240 Hamilton Avenue Palo Alto, California 94301 (415) 322-4555 writers@warthman.com

# Foreword

By Fredrick R. Sporck Director IBM Microelectronics Division—PowerPC Products

IBM's reputation for commitment to technology and innovation is legendary in the computer industry. Over the past two decades, IBM has followed this tradition with its dedication to the development and enhancement of RISC architecture.

With the introduction of the PowerPC architecture, IBM has again recognized the need for supporting its products. In response, IBM has prepared The PowerPC Compiler Writer's Guide. Some of the brightest minds from many companies in the fields of compiler and processor development have combined their efforts in this work. A balanced, insightful examination of the PowerPC architecture and the pipelines implemented by PowerPC processors has yielded a guide giving compiler developers valuable insight into the generation of high-performance code for PowerPC processors.

By taking this step, IBM is equipping readers of The PowerPC Compiler Writer's Guide with the power to harness the potential of the PowerPC revolution. Once again, IBM is stepping forward with dedication to its customers and the powerful backing of its cutting-edge architecture.

# Contents

| 1.      | Introduction                                    | 1   |

|---------|-------------------------------------------------|-----|

| 1.1     | RISC Technologies                               | . 1 |

| 1.2     | Compilers and Optimization                      | . 3 |

| 1.3     | Assumptions                                     |     |

| 2.      | Overview of the PowerPC Architecture            | 5   |

| 2.1     | Application Environment                         | . 5 |

| 2.1.1   | 32-Bit and 64-Bit Implementations and Modes     | . 5 |

| 2.1.2   | Register Resources                              |     |

| 2.1.2.1 | Branch                                          | . 7 |

| 2.1.2.2 | Fixed-Point                                     |     |

| 2.1.2.3 | Floating-Point                                  |     |

| 2.1.3   | Memory Models                                   |     |

| 2.1.3.1 | Memory Addressing                               |     |

| 2.1.3.2 | Endian Orientation                              |     |

| 2.1.3.3 | Alignment                                       |     |

| 2.1.4   | Floating-Point                                  |     |

| 2.2     | Instruction Set                                 | 13  |

| 2.2.1   | Optional Instructions                           | 13  |

| 2.2.2   | Preferred Instruction Forms                     |     |

| 2.2.3   | Communication Between Functional Classes        |     |

| 2.2.3.1 | Fixed-Point and Branch Resources                |     |

| 2.2.3.2 | Fixed-Point and Floating-Point Resources        |     |

| 2.2.3.3 | Floating-Point and Branch Resources             | 15  |

| 3.      | Code Selection                                  | 17  |

| 3.1     | Control Flow                                    | 17  |

| 3.1.1   | Architectural Summary                           |     |

| 3.1.1.1 | Link Register                                   |     |

| 3.1.1.2 | Count Register                                  |     |

| 3.1.1.3 | Condition Register                              |     |

| 3.1.2   | Branch Instruction Performance                  |     |

| 3.1.2.1 | Fall-Through Path                               |     |

| 3.1.2.2 | Needless Branch Register and Recording Activity |     |

| 3.1.2.3 | Condition Register Contention                   | 23  |

| 3.1.3   | Uses of Branching                               |     |

| 3.1.3.1 | Unconditional Branches                          |     |

|         |                                                 |     |

| 3.1.3.2  | Conditional Branches                              |      |

|----------|---------------------------------------------------|------|

| 3.1.3.3  | Multi-Way Conditional Branches                    |      |

| 3.1.3.4  | Iteration                                         |      |

| 3.1.3.5  | Procedure Calls and Returns                       |      |

| 3.1.3.6  | Traps and System Calls                            |      |

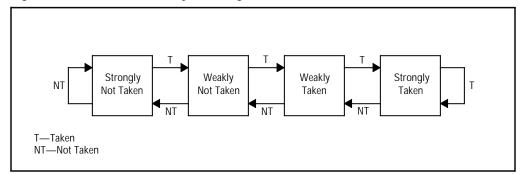

| 3.1.4    | Branch Prediction                                 |      |

| 3.1.4.1  | Default Prediction and Rationale                  |      |

| 3.1.4.2  | Overriding Default Prediction                     |      |

| 3.1.4.3  | Dynamic Branch Prediction                         |      |

| 3.1.5    | Avoiding Branches                                 |      |

| 3.1.5.1  | Computing Predicates                              | . 38 |

| 3.1.5.2  | Conditionally Incrementing a Value by 1           |      |

| 3.1.5.3  | Condition Register Logical                        | . 40 |

| 3.2      | Integer and String Operations                     | . 43 |

| 3.2.1    | Memory Access                                     | . 43 |

| 3.2.1.1  | Single Scalar Load or Store                       |      |

| 3.2.1.2  | Load and Reserve/ Store Conditional               |      |

| 3.2.1.3  | Multiple Scalar Load or Store                     | . 45 |

| 3.2.1.4  | Byte-Reversal Load or Store                       |      |

| 3.2.1.5  | Cache Touch Instructions                          |      |

| 3.2.2    | Computation                                       | . 45 |

| 3.2.2.1  | Setting Status                                    |      |

| 3.2.2.2  | Arithmetic Instructions                           | . 47 |

| 3.2.2.3  | Logical Instructions                              | . 47 |

| 3.2.2.4  | Rotate and Shift Instructions                     | . 47 |

| 3.2.2.5  | Compare Instructions                              | . 48 |

| 3.2.2.6  | Move To/From XER                                  | . 48 |

| 3.2.3    | Uses of Integer Operations                        | . 48 |

| 3.2.3.1  | Loading a Constant into a Register                | . 48 |

| 3.2.3.2  | Endian Reversal                                   | . 49 |

| 3.2.3.3  | Absolute Value                                    | . 50 |

| 3.2.3.4  | Minimum and Maximum                               |      |

| 3.2.3.5  | Division by Integer Constants                     | . 51 |

| 3.2.3.6  | Remainder                                         |      |

| 3.2.3.7  | 32-Bit Implementation of a 64-Bit Unsigned Divide |      |

| 3.2.3.8  | Bit Manipulation                                  |      |

| 3.2.3.9  | Multiple-Precision Shifts                         |      |

| 3.2.3.10 | String and Memory Functions                       | . 68 |

| 3.3      | Floating-Point Operations                         | .72  |

| 3.3.1    | Typing, Conversions and Rounding                  |      |

| 3.3.2    | Memory Access                                     |      |

| 3.3.2.1  | Single-Precision Loads and Stores                 |      |

| 3.3.2.2  | Double-Precision Loads and Stores                 |      |

| 3.3.2.3  | Endian Conversion                                 |      |

| 3.3.2.4  | Touch Instructions                                |      |

| 3.3.3    | Floating-Point Move Instructions                  |      |

| 3.3.4    | Computation                                       |      |

| 3.3.4.1  | Setting Status Bits                               |      |

| 3.3.4.2  | Arithmetic                                        |      |

| 3.3.4.3  | Floating-Point Comparison                         |      |

|          |                                                   |      |

| FPSCR Instructions                                 | 76                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Optional Floating-Point Instructions               | 77                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Square Root                                        | 77                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Storage Access                                     | 77                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Reciprocal Estimate                                | 77                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Reciprocal Square Root Estimate                    | 77                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Selection                                          | 78                                                                                                                                                                                                                                                                                                                                                                                                                         |

| IEEE 754 Considerations                            |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Relaxations                                        | 79                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Data Format Conversion                             | 79                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Floating-Point to Integer                          | 80                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Integer to Floating-Point                          | 83                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rounding to Floating-Point Integer                 | 85                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Floating-Point Branch Elimination                  | 86                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DSP Filters                                        | 92                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Replace Division with Multiplication by Reciprocal | 92                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Floating-Point Exceptions                          | 93                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                    | Optional Floating-Point Instructions<br>Square Root<br>Storage Access<br>Reciprocal Estimate<br>Reciprocal Square Root Estimate<br>Selection<br>IEEE 754 Considerations<br>Relaxations<br>Data Format Conversion<br>Floating-Point to Integer<br>Integer to Floating-Point<br>Rounding to Floating-Point Integer<br>Floating-Point Branch Elimination<br>DSP Filters<br>Replace Division with Multiplication by Reciprocal |

## 4. Implementation Issues

97

| 4.1   | Hardware Implementation Overview |  |

|-------|----------------------------------|--|

| 4.2   | Hazards                          |  |

| 4.2.1 | Data Hazards                     |  |

| 4.2.2 | Control Hazards                  |  |

| 4.2.3 | Structural Hazards               |  |

| 4.2.4 | Serialization                    |  |

| 4.3   | Scheduling                       |  |

| 4.3.1 | Fixed-Point Instructions         |  |

| 4.3.2 | Floating-Point Instructions      |  |

| 4.3.3 | Load and Store Instructions      |  |

| 4.3.4 | Branch Instructions              |  |

| 4.3.5 | List Scheduling Algorithm        |  |

| 4.3.6 | Common Model                     |  |

| 4.3.7 | Examples                         |  |

| 4.4   | Alignment                        |  |

| 4.4.1 | Loads and Stores                 |  |

| 4.4.2 | Fetch Buffer                     |  |

| 4.4.3 | TLB and Cache                    |  |

|       |                                  |  |

## 5. Clever Examples

139

| 5.1 | Sign Function                       | 139 |

|-----|-------------------------------------|-----|

| 5.2 | Transfer of Sign                    | 140 |

| 5.3 | Register Exchange                   | 140 |

| 5.4 | x = y Predicate                     | 141 |

| 5.5 | Clear Least-Significant Nonzero Bit | 141 |

|     |                                     |     |

| 5.6  | Round to a Multiple of a Given Power of 2     | 142 |

|------|-----------------------------------------------|-----|

| 5.7  | Round Up or Down to Next Power of 2           | 142 |

| 5.8  | Bounds Checking                               | 144 |

| 5.9  | Power of 2 Crossing                           | 144 |

| 5.10 | Count Trailing Zeros                          | 145 |

| 5.11 | Population Count                              | 146 |

| 5.12 | Find First String of 1-Bits of a Given Length | 150 |

| 5.13 | Incrementing a Reversed Integer               | 152 |

| 5.14 | Decoding a "Zero Means 2 <sup>n</sup> " Field | 153 |

| 5.15 | 2 <sup>n</sup> in Fortran                     | 154 |

| 5.16 | Integer Log Base 10                           | 154 |

## **Appendices**

| Α.                             | ABI Considerations                                                                                              | 157        |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|

| A.1<br>A.1.1<br>A.1.2<br>A.1.3 | Procedure Interfaces                                                                                            | 158<br>160 |

| A.2<br>A.2.1<br>A.2.2<br>A.2.3 | Procedure Calling Sequence<br>Argument Passing Rules<br>Function Return Values<br>Procedure Prologs and Epilogs | 163<br>165 |

| A.3<br>A.3.1<br>A.3.2<br>A.3.3 | Dynamic Linking<br>Table Of Contents<br>Function Descriptors<br>Out-of-Module Function Calls                    | 167<br>168 |

| В.                             | Summary of PowerPC 6xx Implementations                                                                          | 171        |

| B.1                            | Feature Summary                                                                                                 | 171        |

| B.2<br>B.2.1<br>B.2.2          | Serialization<br>PowerPC 603e Processor Classifications<br>PowerPC 604 Processor Classifications                | 174        |

| B.3                            | Instruction Timing                                                                                              | 175        |

| B.4                            | Misalignment Handling                                                                                           | 184        |

| C.  | PowerPC Instruction Usage Statistics                     | 187 |

|-----|----------------------------------------------------------|-----|

| C.1 | By Instruction Category                                  | 187 |

| C.2 | By Instruction                                           | 188 |

| C.3 | General Information                                      | 195 |

| D.  | Optimal Code Sequences                                   | 199 |

| D.1 | Comparisons and Comparisons Against Zero                 | 199 |

| D.2 | Negated Comparisons and Negated Comparisons Against Zero | 202 |

| D.3 | Comparison Operators                                     |     |

| D.4 | Sign Manipulation                                        | 205 |

| D.5 | Comparisons with Addition                                | 206 |

| D.6 | Bit Manipulation                                         | 208 |

| E.  | Glossary                                                 | 209 |

| F.  | Bibliography and References                              | 235 |

| F.1 | Bibliography                                             | 235 |

| F.2 | References                                               | 235 |

| G.  | Index                                                    | 237 |

# Figures

| Figure 2-1.  | Application Register Sizes                                       | . 6 |

|--------------|------------------------------------------------------------------|-----|

| Figure 2-2.  | Floating-Point Application Control Fields                        |     |

| Figure 3-1   | if-else Code Example                                             | 25  |

| Figure 3-2.  | C Switch: if-else Code Sequence                                  | 26  |

| Figure 3-3.  | C Switch: Range Test Code Sequence                               |     |

| Figure 3-4.  | C Switch: Table Lookup Code Sequence                             |     |

| Figure 3-5.  | strlen Code Example                                              | 29  |

| Figure 3-6.  | Branch-On-Count Loop: Simple Code Example                        | 30  |

| Figure 3-7.  | Branch-On-Count Loop: Variable Number of Iterations Code Example | 30  |

| Figure 3-8.  | Branch-On-Count Loop: Variable Range and Stride Code Example     |     |

| Figure 3-9.  | Compound Latch Point Code Example                                | 32  |

| Figure 3-10. | Function Call Code Example—C Source                              |     |

| Figure 3-11. | Relative Call to foo Code Sequence                               | 33  |

| Figure 3-12. | Call to foo Via Pointer Code Sequence                            | 34  |

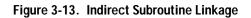

| Figure 3-13. | Indirect Subroutine Linkage                                      | 35  |

|              | Conditional Return Code Example                                  |     |

| Figure 3-15. | Predicate Calculation: Branching Code Sequence                   | 38  |

| Figure 3-16. | Predicate Calculation: Condition-Register Logical Code Sequence  | 38  |

| Figure 3-17. | Predicate Calculation: Fixed-Point-Operation Code Sequence       | 38  |

|              | Arithmetic Expressions for Boolean Predicates                    |     |

|              | Conditionally Incrementing a Value by 1 Code Example             |     |

| Figure 3-20. | Complex Condition Code Example                                   | 41  |

|              | C Switch: Condition Register Logical Code Example                |     |

|              | Scalar Load Instructions                                         |     |

|              | Scalar Store Instructions                                        |     |

|              | Endian Reversal of a 4KB Block of Data Code Sequence             |     |

|              | Absolute Value Code Sequence                                     |     |

|              | Unsigned Maximum of a and b Code Sequence                        |     |

|              | Signed Maximum of a and b Code Sequence                          |     |

|              | Signed Divide by 3 Code Sequence                                 |     |

|              | Signed Divide by 5 Code Sequence                                 |     |

|              | Signed Divide by 7 Code Sequence                                 |     |

|              | Signed Divide by -7 Code Sequence                                |     |

|              | Unsigned Divide by 3 Code Sequence                               |     |

|              | Unsigned Divide by 7 Code Sequence                               |     |

|              | Signed Division Magic Number Computation Code Sequence           |     |

|              | Unsigned Division Magic Number Computation Code Sequence         |     |

|              | Some Magic Numbers for 32-Bit Operations                         |     |

|              | Some Magic Numbers for 64-Bit Operations                         |     |

|              | 32-Bit Signed Remainder Code Sequence                            |     |

| Figure 3-39. | 32-Bit Unsigned Remainder Code Sequence                          | 61  |

| 32-Bit Implementation of 64-Bit Unsigned Division Code Sequence | 62          |  |

|-----------------------------------------------------------------|-------------|--|

| Structure x                                                     |             |  |

| Code sequences to Extract Bit Fields                            |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

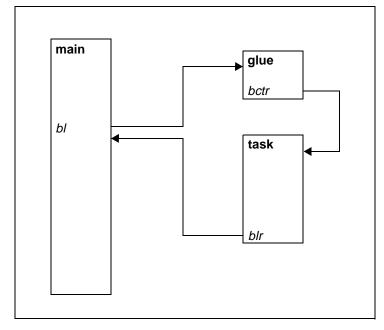

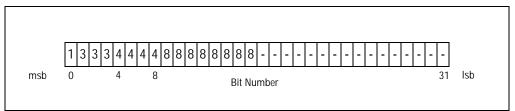

| Code Sequence to Shift 3 Words Left When sh < 64                | 67          |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

|                                                                 |             |  |

| Basic Block Code Example: Scheduled for PowerPC 604 Processor   | 127         |  |

|                                                                 | Structure x |  |

| Figure 4-21. | Dependent Arithmetic-Conditional Assignments Example                  | 129 |  |

|--------------|-----------------------------------------------------------------------|-----|--|

| Figure 4-22. | Rescheduled Dependent Arithmetic-Conditional Assignments Example      |     |  |

| Figure 4-23. | Basic Matrix Multiply Kernel Code Example                             |     |  |

| Figure 4-24. | Matrix Multiply Code Example—Scheduled for PowerPC 604 Processor 12   |     |  |

|              | Nested Loops: Touch Instruction Example                               |     |  |

| Figure 5-1.  | Sign Function Code Sequence                                           |     |  |

| Figure 5-2.  | Fortran ISIGN Function Code Sequence                                  |     |  |

| Figure 5-3.  | Register Exchange Code Sequence                                       |     |  |

| Figure 5-4.  | "x = y" Predicate Code Sequence                                       |     |  |

| Figure 5-5.  | Clear Least-Significant Nonzero Bit Code Sequence                     |     |  |

| Figure 5-6.  | Test for 0 or a Power of 2 Code Sequence                              |     |  |

| Figure 5-7.  | Round Up to a Multiple of 8 Code Sequence                             |     |  |

| Figure 5-8.  | Values of flp2(x) and clp2(x)                                         |     |  |

| Figure 5-9.  | flp2(x) Code Sequence                                                 |     |  |

| •            | clp2(x) Code Sequence                                                 |     |  |

|              | Detect Page Boundary Crossing Code Sequence                           |     |  |

|              | Count Trailing Zeros Code Sequence                                    |     |  |

| Figure 5-13. | Number of Powers of 2 Code Sequence                                   | 146 |  |

| •            | Branch-Free Population Count Code Sequence                            |     |  |

| •            | Branching Population Count Code Sequence                              |     |  |

| •            | Alternative Population Count Code Sequence                            |     |  |

|              | Detect First String of n 1-Bits Code Sequence                         |     |  |

| Figure 5-18. | Incrementing a Reversed Integer Code Sequence                         | 153 |  |

|              | 2 <sup>n</sup> in Fortran Code Sequence                               |     |  |

| Figure 5-20. | Integer Log Base 10 Code Sequence                                     | 155 |  |

| Figure A-1.  | AIX ABI Register Usage Conventions                                    | 159 |  |

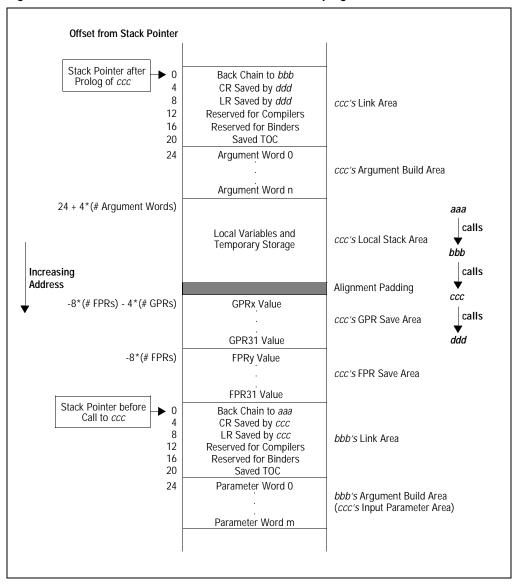

| Figure A-2.  | Relevant Parts of the Run-Time Stack for Subprogram ccc               | 162 |  |

| Figure A-3.  | Argument Passing for foo1                                             | 164 |  |

| Figure A-4.  | Argument Passing for foo2                                             | 164 |  |

| Figure A-5.  | Function Descriptor                                                   | 168 |  |

| Figure A-6.  | main: Function-Calling Code Example                                   | 169 |  |

| Figure A-7.  | ptrgl Routine Code Sequence                                           | 170 |  |

| Figure A-8.  | glink_printf Code Sequence                                            | 170 |  |

| Figure B-1.  | PowerPC 6xx Processor Features                                        | 172 |  |

| Figure B-2.  | Branch Instructions                                                   | 176 |  |

| Figure B-3.  | Load and Store Instructions                                           | 176 |  |

| Figure B-4.  | Cache Control Instructions                                            | 178 |  |

| Figure B-5.  | Fixed-Point Computational Instructions                                | 178 |  |

| Figure B-6.  | Floating-Point Instructions                                           |     |  |

| Figure B-7.  | Optional Instructions                                                 | 182 |  |

| Figure B-8.  | Number of Accesses for Misaligned Operands                            |     |  |

| Figure C-1.  | Instruction Frequency in Integer SPEC92 Benchmarks                    |     |  |

| Figure C-2.  | Instruction Frequency in Floating-Point SPEC92 Benchmarks             |     |  |

| Figure C-3.  | Most Frequently Used Instructions in Integer SPEC92 Benchmarks        |     |  |

| Figure C-4.  | Most Frequently Used Instructions in Floating-Point SPEC92 Benchmarks |     |  |

| Figure C-5.  | PowerPC Instruction Usage in SPEC92 Benchmarks                        |     |  |

# Preface

#### **Purpose and Audience**

This book describes, mainly by coding examples, the code patterns that perform well on PowerPC processors. The book will be particularly helpful to compiler developers and application-code specialists who are already familiar with optimizing compiler technology and are looking for ways to exploit the PowerPC architecture. It will also be helpful to application programmers who need to understand and tune the output of PowerPC compilers and to faculty members and graduate students specializing in the study of compilers. We assume that compiler developers have already developed a compiler front-end and are seeking to develop a PowerPC back-end.

The book does not attempt to teach the average programmer how to write a compiler or the accompanying library routines. Readers seeking this kind of information may wish to acquire some of the publications listed in the references.

The book is a companion to Book I of *The PowerPC Architecture*. Detailed descriptions from *The PowerPC Architecture* are not repeated except in summary form, although we include several references to sections in the specification. The material and instructions described in Books II and III of *The PowerPC Architecture* are, in general, not included because they are primarily of interest to operating-system developers.

#### **Code Examples**

Where possible and useful, the book includes code examples, generalizations of coding approach, and general advice on issues affecting coding decisions. The examples are primarily in PowerPC assembler code, but they may also show related source code (typically C or Fortran). Most of the code examples are chosen to perform well on a generic PowerPC processor, called a Common Model, although advice on coding for specific PowerPC-processor implementations is sometimes included.

Most code examples are from IBM. A few code examples in Chapter 5, "Clever Examples", have been contributed by non-IBM programmers. A few examples are taken from *The PowerPC Architecture* or IBM technical papers. The PowerPC extended mnemonics that are used in the code examples are listed in a table at the end of this preface.

#### Contributors

#### Writers and Editors:

- IBM Editor: Steve Hoxey, IBM Toronto Laboratory

- IBM Editor: Faraydon Karim, IBM Microelectronics Division

- IBM Editor: Bill Hay, IBM Toronto Laboratory

- BIM Editor: Hank Warren, IBM Thomas J. Watson Research Center

- Writer: Philip Dickinson, Warthman Associates

- Independent Editor: Dennis Allison, Stanford University

- Managing Editor: Forrest Warthman, Warthman Associates

Review Comments and/or Code Examples:

- Steve Barnett, Absoft Corporation

- Bob Blainey, IBM Toronto Laboratory

- Patrick Bohrer, IBM Microelectronics Division

- Gary Davidian, Power Computing Corporation

- Kaivalya Dixit, IBM RISC System/6000 Division

- Bill Hay, IBM Toronto Laboratory

- Richard Hooker, IBM Microelectronics Division

- Steve Hoxey, IBM Toronto Laboratory

- Steve Jasik, Jasik Designs

- Faraydon Karim, IBM Microelectronics Division

- Lena Lau, IBM Toronto Laboratory

- Cathy May, IBM Thomas J. Watson Research Center

- John McEnerney, Metrowerks, Inc.

- Dave Murrell, IBM Microelectronics Division

- Tim Olson, Apple Computer, Inc.

- Brett Olsson, IBM System Technology and Architecture Division

- Tom Pennello, MetaWare, Inc.

- Mike Peters, IBM PowerPC Performance Group

- Brian Peterson, IBM Microelectronics Division

- Nam H. Pham, IBM Microelectronics Division

- Warren Ristow, Apogee Software, Inc.

- Alex Rosenberg, Apple Computer, Inc.

- Tim Saunders, IBM Microelectronics Division

- Ed Silha, IBM System Technology and Architecture Division

- Fred Strietelmeier, IBM System Technology and Architecture Division

- S. Surya, IBM PowerPC Performance Group

- Maureen Teodorovich, IBM Microelectronics Division

- Hank Warren, IBM Thomas J. Watson Research Center

- Pete Wilson, Groupe Bull

#### Notation

| 0:31                | Bits 0 through 31 of a big-endian word.                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ra                  | General-purpose register <i>a</i> , where <i>a</i> is a number or letter other than <i>A</i> .                                                                                                                                   |

| RA                  | General-purpose register indicated by the field 11:15 in the instruction encoding for load/store instructions that do not update and <i>addi</i> and <i>addis</i> instructions. If this field indicates R0, the value 0 is used. |

| FRa <sub>0:36</sub> | Floating-point register <i>a</i> , big-endian bits 0:36.                                                                                                                                                                         |

| cr <i>n</i>         | Condition Register field <i>n</i> .                                                                                                                                                                                              |

| cr <i>n[lt</i> ]    | The <i>It</i> bit in Condition Register field <i>n</i> . The following table summa-                                                                                                                                              |

#### **Condition Register Field Bits**

in this book.

| Bit Name | Bit Position in<br>Field | Description                                                          |

|----------|--------------------------|----------------------------------------------------------------------|

| lt       | 0                        |                                                                      |

| gt       | 1                        | The result of a recording fixed-<br>point operation or a fixed-point |

| eq       | 2                        | compare.                                                             |

| SO       | 3                        |                                                                      |

| fx       | 0 in CR1                 |                                                                      |

| fex      | 1 in CR1                 | The result of a recording floating-                                  |

| VX       | 2 in CR1                 | point operation.                                                     |

| ох       | 3 in CR1                 |                                                                      |

| fl       | 0                        |                                                                      |

| fg       | 1                        | The result of a floating-point                                       |

| fe       | 2                        | compare operation.                                                   |

| fu       | 3                        |                                                                      |

rizes the names of the bits in the Condition Register fields used

(x) The contents of *x*, where *x* indicates some register or field.

- (RA|0) The contents of general-purpose register *A*, or the value 0 if RA indicates R0.

- 0xFFFF Decimal 65535 (64K) in *hexadecimal* notation.

- 0b0011 Decimal 3 in *binary* notation.

| x    y         | The concatenation of <i>x</i> and <i>y</i> .                                                                                                                                                |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <sup>n</sup> X | <i>x</i> repeated <i>n</i> times.                                                                                                                                                           |

| E              | Is a member of.                                                                                                                                                                             |

| &              | Logical AND.                                                                                                                                                                                |

|                | Logical OR.                                                                                                                                                                                 |

| $\oplus$       | Logical XOR.                                                                                                                                                                                |

| -              | Logical NOT.                                                                                                                                                                                |

| =              | Logical equivalence.                                                                                                                                                                        |

| instruction    | A PowerPC instruction mnemonic.                                                                                                                                                             |

| [.]            | An optional period at the end of a PowerPC instruction mne-<br>monic. It causes condition codes for the result to be stored in the<br>Condition Register (CR).                              |

| [0]            | An optional "o" at the end of a PowerPC instruction mnemonic. It causes the SO (summary overflow) and OV (overflow) bits of the fixed-point exception register (XER) to reflect the result. |

Acronyms, words, and phrases are defined in the Glossary at the back of the book. The following table gives the equivalent mnemonic for extended mnemonics used in this book:

| Extended Mnemonic                                                                                                                                                                                                                                           | Equivalent Mnemonic           | Name                                                 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------|--|

| Extended Winemonic                                                                                                                                                                                                                                          |                               |                                                      |  |

| bctr                                                                                                                                                                                                                                                        | bcctr 20,bi                   | Branch Unconditionally to CTR                        |  |

| bctrl                                                                                                                                                                                                                                                       | bcctrl 20,bi                  | Branch Unconditionally to CTR Setting LR             |  |

| bdnz target                                                                                                                                                                                                                                                 | bc 16,bi,target               | Decrement CTR,<br>Branch If CTR ≠ 0                  |  |

| bdnzf target                                                                                                                                                                                                                                                | bc 8,bi,target                | Decrement CTR, Branch If CTR ≠ 0 and Condition False |  |

| bdz target                                                                                                                                                                                                                                                  | bc 18,bi,target               | Decrement CTR, Branch If<br>CTR = 0                  |  |

| beq crn,target                                                                                                                                                                                                                                              | <pre>bc 12,4*n+2,target</pre> | Branch If Equal To                                   |  |

| LR—Link Register<br>CTR—Count Register<br>crn—Condition Register field n<br>xx—Alphabetic code for bit in Condition Register field (see previous table)<br>UI—Unsigned 14-bit intermediate<br>SI—Signed 14-bit intermediate<br>bi—Bit in Condition Register |                               |                                                      |  |

#### Extended Mnemonics Used in This Book

| <b>Extended Mnemonics Used in</b> | This Book | (continued) | ) |

|-----------------------------------|-----------|-------------|---|

|-----------------------------------|-----------|-------------|---|

| Extended Mnemonic                                                                                                                                                                                         | Equivalent Mnemonic                                 | Name                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------|

| bf crn[xx],target                                                                                                                                                                                         | ,                                                   | Branch If Condition False             |

| bge crn,target                                                                                                                                                                                            | bc 4,4*n,target                                     | Branch If Greater Than Or Equal<br>To |

| bgt crn,target                                                                                                                                                                                            | <pre>bc 12,4*n+1,target</pre>                       | Branch If Greater Than                |

| bgtlr cr <i>n</i>                                                                                                                                                                                         | bclr 12,4*n+1                                       | Branch If Greater Than to LR          |

| ble crn, target                                                                                                                                                                                           | <pre>bc 4,4*n+1,target</pre>                        | Branch If Less Than Or Equal To       |

| blr                                                                                                                                                                                                       | bclr 20,bi                                          | Branch Unconditionally to LR          |

| blt crn,target                                                                                                                                                                                            | <pre>bc 12,4*n,target</pre>                         | Branch If Less Than                   |

| bne cr <i>n</i> ,target                                                                                                                                                                                   | <pre>bc 4,4*n+2,target</pre>                        | Branch If Not Equal To                |

| <pre>bt crn[xx],target</pre>                                                                                                                                                                              | bc 12,bi,target                                     | Branch If True                        |

| cmplw crn,Ra,Rb                                                                                                                                                                                           | cmpl crn,0,Ra,Rb                                    | Compare Logical Word                  |

| cmplwi crn,Ra,UI                                                                                                                                                                                          | cmpli crn,0,Ra,UI                                   | Compare Logical Word Immedi-<br>ate   |

| cmpw crn,Ra,Rb                                                                                                                                                                                            | cmp crn,0,Ra,Rb                                     | Compare Word                          |

| cmpwi cr <i>n</i> ,Ra,SI                                                                                                                                                                                  | cmpi crn,0,Ra,SI                                    | Compare Word Immediate                |

| li Rx,value                                                                                                                                                                                               | addi Rx,0,value                                     | Load Immediate                        |

| lis Rx,value                                                                                                                                                                                              | addis Rx,0,value                                    | Load Immediate Shifted                |

| mfctr Rx                                                                                                                                                                                                  | mfspr Rx,9                                          | Move From CTR                         |

| mflr Rx                                                                                                                                                                                                   | mfspr Rx,8                                          | Move From LR                          |

| mfxer Rx                                                                                                                                                                                                  | mfspr Rx,1                                          | Move From XER                         |

| mr Rx,Ry                                                                                                                                                                                                  | or Rx,Ry,Ry<br>(ori Rx,Ry,0)                        | Move Register                         |

| mtctr Rx                                                                                                                                                                                                  | mtspr 9,Rx                                          | Move To CTR                           |

| mtlr Rx                                                                                                                                                                                                   | mtspr 8,Rx                                          | Move To LR                            |

| mtxer Rx                                                                                                                                                                                                  | mtspr 1,Rx                                          | Move To XER                           |

| not Rx,Ry                                                                                                                                                                                                 | nor Rx,Ry,Ry                                        | Logical NOT                           |

| slwi Rx,Ry,n                                                                                                                                                                                              | rlwinm Rx,Ry,n,0,31-n                               | Shift Left Immediate                  |

| srwi Rx,Ry,n                                                                                                                                                                                              | rlwinm Rx,Ry,32-n,n,31                              | Shift Right Immediate                 |

| sub Rx,Ry,Rz                                                                                                                                                                                              | <pre>subf Rx,Rz,Ry</pre>                            | Subtract                              |

| subi Rx,Ry,value                                                                                                                                                                                          | addi Rx,Ry,-value                                   | Subtract Immediate                    |

| LR—Link Register<br>CTR—Count Register<br>crn—Condition Register field<br>xx—Alphabetic code for bit in<br>UI—Unsigned 14-bit intermediat<br>SI—Signed 14-bit intermediat<br>bi—Bit in Condition Register | Condition Register field (see previous tal<br>liate | ble)                                  |

Chapter 1

# Introduction

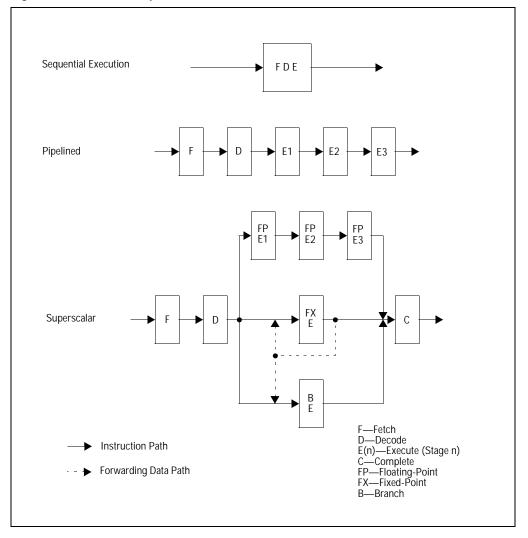

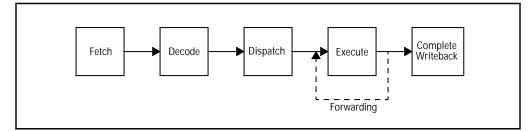

High-performance computer systems depend on good hardware design coupled with powerful compilers and operating systems. Although announced in 1991, the PowerPC architecture represents the end product of nearly 20 years of evolution starting with work on the 801 system at IBM. From the beginning, advanced hardware and software techniques were intermingled to develop first RISC and then superscalar computer systems. This guide describes how a compiler may select and schedule code that performs to the potential of the architecture.

#### **1.1 RISC Technologies**

The time required to execute a program is the product of the path length (the number of instructions), the number of cycles per instruction, and the cycle time. These three variables interact with one another. For example, reducing the cycle time reduces the window of time in which useful work can be performed, so the execution of a complex instruction may be unable to finish. Then, the function of the complex instruction must be separated into multiple simpler instructions, increasing the path length. Identifying the optimal combination of these variables in the form of an instruction set architecture, therefore, represents a challenging problem whose solution depends on the hardware technology and the software requirements.

Historically, CISC architectures evolved in response to the limited availability of memory because complex instructions result in smaller programs. As technology improved, memory cost dropped and access times decreased, so the decode and execution of the instructions became the limiting steps in instruction processing. Work at IBM, Berkeley, and Stanford demonstrated that performance improved if the instruction set was simple and instructions required a small number of cycles to execute, preferably one cycle. The reduction in cycle time and number of cycles needed to process an instruction were a good trade-off against the increased path length. Development along these RISC lines continued at IBM and elsewhere. The physical design of the computer was simplified in exchange for increased hardware management by compilers and operating systems.

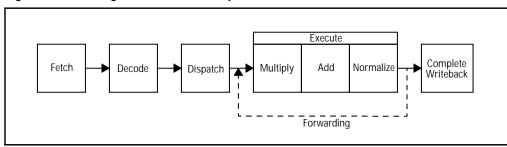

The work at IBM led to the development of the POWER™ architecture, which implemented parallel instruction (superscalar) processing, introduced some compound instructions to reduce instruction path lengths in critical areas, incorporated floatingpoint as a first-class data type, and simplified the architecture as a compiler target. Multiple pipelines permitted the simultaneous execution of different instructions, effectively reducing the number of cycles required to execute each instruction. The POWER architecture refined the original RISC approach by improving the mapping of the hardware architecture to the needs of programming languages. The functionality of key instructions was increased by combining multiple operations in the same instruction: the load and store with update instructions, which perform the access and load the effective address into the base register; the floating-point multiply-add instructions; the branch-on-count instructions, which decrement the Count Register and test the contents for zero: or the rotate-mask instructions. This increased functionality significantly reduced the path length for critical areas of code, such as loops, at the expense of moderately longer pipeline stages.

The POWER instruction set architecture and the hardware implementation were developed together so that they share a common partitioning based on function, minimizing the interaction between different functions. By arranging the instruction set in this way, the compiler could better arrange the code so that there were fewer inter-instruction dependencies impeding superscalar dispatch. The role of the compiler became more important because it generated code that could extract the performance potential of this superscalar hardware.

IBM, Motorola, and Apple jointly defined the PowerPC architecture as an evolution of the POWER architecture. The modifications to the POWER architecture include:

- Clearer distinctions between the architecture and implementations.

- Simplifications and specifications to improve high-speed superscalar and single-chip performance.

- 32-bit and 64-bit architectures.

- Memory-consistency model for symmetric multiprocessing.

#### 1.2 Compilers and Optimization

The quality of code generated by a compiler is measured in terms of its size and execution speed. The compiler must balance these factors for the particular programming environment. The quality is most profoundly affected by the choice of algorithm and data structures, choices which are the province of the individual programmer. Given the algorithm and data structures, guality depends upon a collusion between the compiler, the processor architecture, and the specific implementation to best exploit the resources of the computer system. Modern processors rely upon statistical properties of the programs and upon the ability of the compiler to transform and schedule the specification of the algorithm in a semantically equivalent way so as to improve the performance of individual programs. Today, most programming is done in a high-level language. The compilers for these languages are free to generate the best possible machine code within the constraint that the semantics of the language are preserved. This book concentrates on compilers for procedure-oriented languages, such as C or Fortran.

Optimizations are traditionally classified as machine-independent or machine-dependent. Compilers usually perform machine-independent optimizations by transforming an intermediate language version of the program into an equivalent optimized program, also expressed in the intermediate language. The choice of optimizations normally considered machine-independent and their order of application, however, may actually be machine-dependent. Most classical compiler issues, including the front-end syntactic and semantic checks, intermediate language, and most machineindependent optimizations are not covered here; they are described elsewhere in the literature. This book focuses principally on implementation-dependent optimizations specific to the PowerPC architecture.

Machine-dependent optimizations require detailed knowledge of the processor architecture, the Application Binary Interface (ABI) and the processor implementation. Detailed issues of code choice depend mostly on the architecture. Typical compilers examine the intermediate representation of the program and select semantically equivalent machine instructions. The ABI is a convention that allows programs to function in a particular programming environment, but restricts the type of code that a compiler can emit in many contexts. Two PowerPC compilers that target different operating environments may generate quite different optimized code for the same program. Machine-dependent optimizations, such as program layout, scheduling, and alignment considerations, depend on the implementation of the architecture. In the case of the PowerPC architecture, there are a number of implementations, each with different constraints on these optimizations.

#### **1.3 Assumptions**

The assumptions made in this book include:

- Familiarity with the PowerPC Architecture—We assume that you know the PowerPC architecture as described in The PowerPC Architecture: A Specification for a New Family of RISC Processors (hereafter known as The PowerPC Architecture). We make frequent references to sections in this book.

- Common Model—Unless otherwise stated, we assume that you are generating code for the PowerPC Common Model implementation, which is described in Section 4.3.6 on page 117. The Common Model is a fictional PowerPC implementation whose scheduled code should perform well, though perhaps not optimally, on all PowerPC implementations. Optimizations for particular processors are mentioned where appropriate. We consider only uniprocessor systems. Multiprocessing systems lie beyond the scope of this work.

- Compiler Environment—We assume that you have already developed a compiler front-end with an intermediate language connection to an optimizing and code-emitting back-end, or that you are directly optimizing application programs in an assembler. This book discusses only the optimizing and codeemitting back-end that creates PowerPC object files.

# **Overview of the PowerPC Architecture**

Books I through III of *The PowerPC Architecture* describe the instruction set, virtual environment, and operating environment, respectively. The user manual for each processor specifies the implementation features of that processor. In this book, the term *PowerPC architecture* refers to the contents of Books I through III. The compiler writer is concerned principally with the contents of Book I: PowerPC User Instruction Set Architecture.

#### 2.1 **Application Environment**

The application environment consists of resources accessible from the problem state, which is the user mode (the PR bit in the Machine State Register is set). The PowerPC architecture is a load-store architecture that defines specifications for both 32-bit and 64-bit implementations. The instruction set is partitioned into three functional classes: branch, fixed-point and floating-point. The registers are also partitioned into groups corresponding to these classes; that is, there are condition code and branch target registers for branches, Floating-Point Registers for floating-point operations, and General-Purpose Registers for fixed-point operations. This partition benefits superscalar implementations by reducing the interlocking necessary for dependency checking. The explicit indication of all operands in the instructions, combined with the partitioning of the PowerPC architecture into functional classes, exposes dependences to the compiler. Although instructions must be word (32-bit) aligned, data can be misaligned within certain implementation-dependent constraints. The floating-point facilities support compliance to the IEEE 754 Standard for Binary Floating-Point Arithmetic (IEEE 754).

2.1.1 **32-Bit and 64-Bit** Implementations and Modes The PowerPC architecture includes specifications for both 32and 64-bit implementations. In 32-bit implementations, all application registers have 32 bits, except for the 64-bit Floating-Point Registers, and effective addresses have 32 bits. In 64-bit implementations, all application registers are 64-bits long—except for the 32-bit Condition Register, FPSCR, and XER—and effective addresses have 64 bits. Figure 2-1 shows the application register sizes in 32-bit and 64-bit implementations.

| Registers                                  | 32-Bit Implementation<br>Size (Bits) | 64-Bit Implementation<br>Size (Bits) |  |

|--------------------------------------------|--------------------------------------|--------------------------------------|--|

| Condition Register                         | 32                                   | 32                                   |  |

| Link Register and Count Register           | 32                                   | 64                                   |  |

| General-Purpose Registers                  | 32                                   | 64                                   |  |

| fixed-point Exception Register             | 32                                   | 32                                   |  |

| Floating-Point Registers                   | 64                                   | 64                                   |  |

| Floating-Point Status and Control Register | 32                                   | 32                                   |  |

Figure 2-1. Application Register Sizes

Both 32-bit and 64-bit implementations support most of the instructions defined by the PowerPC architecture. The 64-bit implementations support all the application instructions supported 32-bit implementations as well as the following application instructions: load doubleword, store doubleword, load word algebraic, multiply doubleword, divide doubleword, rotate doubleword, sign extend word, and convert doubleword integer to a floating-point value.

The 64-bit implementations have two modes of operation determined by the 64-bit mode (SF) bit in the Machine State Register: 64-bit mode (SF set to 1) and 32-bit mode (SF cleared to 0), for compatibility with 32-bit implementations. Application code for 32-bit implementations executes without modification on 64-bit implementations running in 32-bit mode, yielding identical results. All 64-bit implementation instructions are available in both modes. Identical instructions, however, may produce different results in 32-bit and 64-bit modes:

- Addressing—Although effective addresses in 64-bit implementations have 64 bits, in 32-bit mode, the high-order 32 bits are ignored during data access and set to zero during instruction fetching. This modification of the high-order bits of the address might produce an unexpected jump following the transition from 64-bit mode to 32-bit mode.

- Status Bits—The register result of arithmetic and logical instructions is independent of mode, but setting of status bits depends on the mode. In particular, recording, carry-bit-setting, or overflow-bit-setting instruction forms write the status

bits relative to the mode. Changing the mode in the middle of a code sequence that depends on one of these status bits can lead to unexpected results. *Count Register*—The entire 64-bit value in the Count Register of a 64-bit implementation is decremented, even though conditional branches in 32-bit mode only test the low-order 32 bits for zero.

The PowerPC architecture identifies each register with a functional class, and most instructions within a class use only the reg-

2.1.2 **Register Resources** The PowerPC architecture identifies each register with a functional class, and most instructions within a class use only the registers identified with that class. Only a small number of instructions transfer data between functional classes. This separation of processor functionality reduces the hardware interlocking needed for parallel execution and exposes register dependences to the compiler.

2.1.2.1 Branch The Branch-Processing Unit includes the Condition Register, Link Register (LR) and Count Register (CTR):

- Condition Register—Conditional comparisons are performed by first setting a condition code in the Condition Register with a compare instruction or with a recording instruction. The condition code is then available as a value or can be tested by a branch instruction to control program flow. The 32-bit Condition Register consists of eight independent 4-bit fields grouped together for convenient save or restore during a context switch. Each field may hold status information from a comparison, arithmetic, or logical operation. The compiler can schedule Condition Register fields to avoid data hazards in the same way that it schedules General-Purpose Registers. Writes to the Condition Register occur only for instructions that explicitly request them; most operations have recording and non-recording instruction forms.

- Link Register—The Link Register may be used to hold the effective address of a branch target. Branch instructions with the link bit (LK) set to one copy the next instruction address into the Link Register. A Move To Special-Purpose Register instruction can copy the contents of a General-Purpose Register into the Link Register.

- Count Register—The Count Register may be used to hold either a loop counter or the effective address of a branch target. Some conditional-branch instruction forms decrement the Count Register and test it for a zero value. A Move To Special-Purpose Register instruction can copy the contents of a General-Purpose Register into the Count Register.

- 2.1.2.2 Fixed-Point The Fixed-Point Unit includes the General-Purpose Register file and the Fixed-Point Exception Register (XER):

|                           | <ul> <li>General-Purpose Registers—Fixed-point instructions operate on the full width of the 32 General-Purpose Registers. In 64-bit implementations, the instructions are mode-independent, except that in 32-bit mode, the processor uses only the low-order 32 bits for determination of a memory address and the carry, overflow, and record status bits.</li> <li>XER—The XER contains the carry and overflow bits and the byte count for the move-assist instructions. Most arithmetic operations have carry-bit–setting and overflow-bit–setting instruction forms.</li> </ul>                                                                                                                                                                        |